# FIFO Input/Output Interface Unit

#### Features

- 128-byte FIFO buffer provides asynchronous bidirectional CPU/CPU or CPU/peripheral interface, expandable to any width in byte increments by use of multiple Z8060 FIO's

- Interlocked 2-Wire or 3-Wire Handshake logic port mode; Z-BUS or non-Z-BUS interface.

- Pattern-recognition logic stops DMA transfers and/or interrupts CPU; preset byte count can initiate variable-length DMA transfers.

- Seven sources of vectored/nonvectored interrupt which include pattern-match, byte count, empty or full buffer status; a dedicated "mailbox" register with interrupt capability provides CPU/CPU communication.

- REQUEST/WAIT lines control high-speed data transfers.

- All functions are software controlled via directly addressable read/write registers.

### General Description

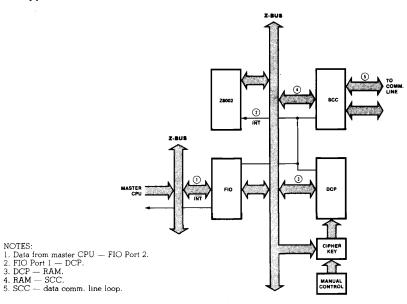

The Z8038 FIO provides an asynchronous 128-byte FIFO buffer between two CPUs or between a CPU and a peripheral device. This buffer interface expands to a 16-bit or wider data path and expands in depth to add as many Z8060 FIFOs (and an additional FIO) as are needed.

The FIO manages data transfers by assuming Z-BUS, non-Z-BUS microprocessor (a generalized microprocessor interface), Interlocked

2-Wire Handshake, and 3-Wire Handshake operating modes. These modes interface dissimilar CPUs or CPUs and peripherals running under differing speeds or protocols, allowing asynchronous data transactions and improving I/O overhead by as much as two orders of magnitude. Figures 1 and 2 show how the signals controlling these operating modes are mapped to the FIO pins.

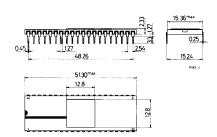

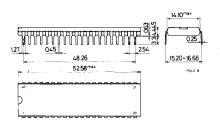

Figure 1. Logic Functions

Figure 2. Pin Configuration

#### General Description (Continued)

The FIO supports the Z-BUS interrupt protocols, generating seven sources of interrupts upon any of the following events: a write to a message register, change in data direction, pattern match, status match, over/underflow error, buffer full and buffer empty status. Each interrupt source can be enabled or disabled, and can also place an interrupt vector on the port address/data lines.

The data transfer logic of the FIO has been

specially designed to work with DMA (Direct Memory Access) devices for high-speed transfers. It provides for data transfers to or from memory each machine cycle, while the DMA device generates memory address and control signals. The FIO also supports the variably sized block length, improving system throughput when multiple variable length messages are transferred amongst several sources.

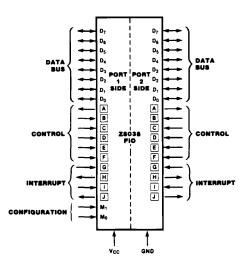

Figure 3. FIO Block Diagram

#### Functional Description

**Operating Modes.** Ports 1 and 2 operate in any of twelve combinations of operating modes, listed in Table 2. Port 1 functions in either the Z-BUS or non-Z-BUS microprocessor modes, while Port 2 functions in Z-BUS, non-Z-BUS, Interlocked 2-Wire Handshake, and 3-Wire Handshake modes. Table 1 describes the signals and their corresponding pins in each of these modes.

The pin diagrams of the FIO are identical, except for two pins on the Port 1 side, which select that port's operating mode. Port 2's operating mode is programmed by two bits in Port 1's Control register 0. Table 2 describes the combinations of operating modes; Table 3 describes the control signals mapped to pins A-J in the five possible operating modes.

## Functional Description (Continued)

| Control<br>Signal<br>Pins | Z-BUS<br>Low Byte | Z-BUS<br>High Byte | Non-Z-BUS        | Interlocked<br>HS Port* | 3-Wire<br>HS Port* |

|---------------------------|-------------------|--------------------|------------------|-------------------------|--------------------|

| A                         | REQ/WT            | REQ/WT             | REQ/WT           | RFD/DAV                 | RFD/DAV            |

| В                         | DMASTB            | DMASTB             | DACK             | ACKIN                   | DAV/DAC            |

| C                         | DS                | DS                 | RD               | FULL                    | DAC/RFD            |

| D                         | $R/\overline{W}$  | R/W                | WR               | EMPTY                   | <b>EMPTY</b>       |

| E                         | CS                | CS                 | CE               | CLEAR                   | CLEAR              |

| F                         | ĀS                | AS                 | $C/\overline{D}$ | DATA DIR                | DATA DIR           |

| G                         | INTACK            | A <sub>0</sub>     | INTACK           | INO                     | IN <sub>0</sub>    |

| H                         | IEO               | Al                 | IEO              | $out_1$                 | $out_1$            |

| 1                         | IEI               | A <sub>2</sub>     | IEI              | ŌĒ                      | ŌĒ                 |

| 1                         | ĪNT               | A <sub>3</sub>     | INT              | OUT3                    | OUT3               |

<sup>\*2</sup> side only.

Table 1. Pin Assignments

| Mode | Mı | M <sub>0</sub> | Bl | B <sub>0</sub> | Port 1          | Port 2           |

|------|----|----------------|----|----------------|-----------------|------------------|

| 0    | 0  | 0              | 0  | 0              | Z-BUS Low Byte  | Z-BUS Low Byte   |

| 1    | 0  | 0              | 0  | 1              | Z-BUS Low Byte  | Non-Z-BUS        |

| 2    | 0  | 0              | 1  | 0              | Z-BUS Low Byte  | 3-Wire Handshake |

| 3    | 0  | 0              | 1  | 1              | Z-BUS Low Byte  | 2-Wire Handshake |

| 4    | 0  | 1              | 0  | 0              | Z-BUS High Byte | Z-BUS High Byte  |

| 5    | 0  | 1              | 0  | 1              | Z-BUS High Byte | Non-Z-BUS        |

| 6    | 0  | 1              | 1  | 0              | Z-BUS High Byte | 3-Wire Handshake |

| 7    | 0  | 1              | 1  | 1              | Z-BUS High Byte | 2-Wire Handshake |

| 8    | 1  | 0              | 0  | 0              | Non-Z-BUS       | Z-BUS Low Byte   |

| 9    | 1  | 0              | 0  | 1              | Non-Z-BUS       | Non-Z-BUS        |

| 10   | 1  | 0              | 1  | 0              | Non-Z-BUS       | 3-Wire Handshake |

| 11   | 1  | 0              | 1  | 1              | Non-Z-BUS       | 2-Wire Handshake |

Table 2. Operating Modes

215

## Functional Description (Continued)

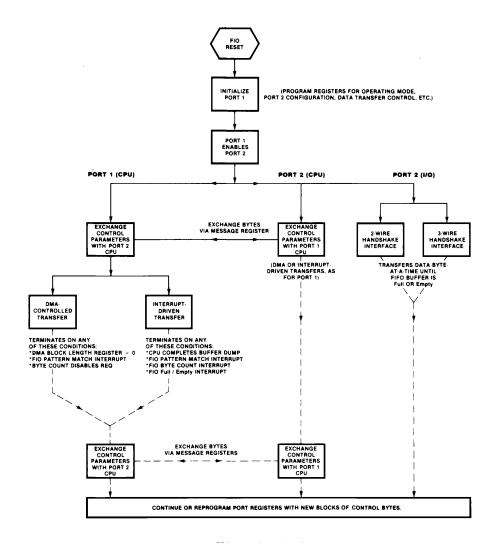

Figure 4. CPU to CPU Configuration

Figure 5. CPU to I/O Configuration

## Pins Common To Both Sides

| Pin<br>Signals | Pin<br>Names   | Pin<br>Numbers | Signal<br>Description                            |

|----------------|----------------|----------------|--------------------------------------------------|

| M <sub>O</sub> | M <sub>0</sub> | 21             | M <sub>1</sub> and M <sub>0</sub> program Port 1 |

| Ml             | $M_1$          | 19             | side CPU interface                               |

| +5 Vdc         | +5 Vdc         | 40             | DC power source                                  |

| GND            | GND            | 20             | DC power ground                                  |

## **Z-BUS Low Byte Mode**

| Pin<br>Signals                                     | Pin<br>Names                   | Pin Nu<br>Po<br>1 |       | Signal<br>Description                                                                                                                 |

|----------------------------------------------------|--------------------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| AD <sub>0</sub> -AD <sub>7</sub><br>(Address/Data) | D <sub>0</sub> -D <sub>7</sub> | 11-18             | 29-22 | Multiplexed bidirectional address/data lines, Z-BUS compatible.                                                                       |

| REQ/WAIT<br>(Request/Wait)                         | A                              | 1                 | 39    | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers. |

| DMASTB<br>(Direct Memory<br>Access Strobe)         | В                              | 2                 | 38    | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                      |

| DS<br>(Data Strobe)                                | С                              | 3                 | 37    | Input, active Low. Provides timing for data transfer to or from FIO.                                                                  |

| R/W<br>(Read/Write)                                | D                              | 4                 | 36    | Input; active High signals CPU read from FIO; active Low signals CPU write to FIO.                                                    |

| CS<br>(Chip Select)                                | E                              | 5                 | 35    | Input, active Low. Enables FIO. Latched on the rising edge of $\overline{AS}$ .                                                       |

| ĀS<br>(Address Strobe)                             | F                              | 6                 | 34    | Input, active Low. Addresses, $\overline{\text{CS}}$ and $\overline{\text{INTACK}}$ sampled while $\overline{\text{AS}}$ Low.         |

| INTACK<br>(Interrupt<br>Acknowledge)               | G                              | 7                 | 33    | Input, active Low. Acknowledges an interrupt. Latched on the rising edge of $\overline{AS}$ .                                         |

| IEO<br>(Interrupt<br>Enable Out)                   | Н                              | 8                 | 32    | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                         |

| IEI<br>(Interrupt<br>Enable In)                    | I                              | 9                 | 31    | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                 |

| INT<br>(Interrupt)                                 | J                              | 10                | 30    | Output, open drain, active Low. Signals FIO interrupt request to CPU.                                                                 |

Table 3. Signal/Pin Descriptions

## **Z-BUS High Byte Mode**

| Pin<br>Signals                                     | Pin<br>Names                   | Pin Nu<br>Po<br>1 |       | Signal<br>Description                                                                                                                 |

|----------------------------------------------------|--------------------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| AD <sub>0</sub> -AD <sub>7</sub><br>(Address/Data) | D <sub>0</sub> -D <sub>7</sub> | 11-18             | 29-22 | Multiplexed bidirectional address/data lines, Z-BUS compatible.                                                                       |

| REQ/WAIT<br>(Request/Wait)                         | A                              | 1                 | 39    | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfers. |

| DMASTB<br>(Direct Memory<br>Access Strobe)         | В                              | 2                 | 38    | Input, active Low. Strobes DMA data to and from the FIFO buffer.                                                                      |

| DS<br>(Data Strobe)                                | С                              | 3                 | 37    | Input, active Low. Provides timing for transfer of data to or from FIO.                                                               |

| R/W<br>(Read/Write)                                | D                              | 4                 | 36    | Input, active High. Signals CPU read from FIO; active Low signals CPU write to FIO.                                                   |

| CS<br>(Chip Select)                                | E                              | 5                 | 35    | Input, active Low. Enables FIO. Latched on the rising edge of $\overline{\text{AS}}.$                                                 |

| AS<br>(Address Strobe)                             | F                              | 6                 | 34    | Input, active Low. Addresses, $\overline{\text{CS}}$ and $\overline{\text{INTACK}}$ are sampled while $\overline{\text{AS}}$ is Low.  |

| A <sub>0</sub><br>(Address Bit 0)                  | G                              | 7                 | 33    | Input, active High. With $A_1$ , $A_2$ , and $A_3$ , addresses FIO internal registers.                                                |

| A <sub>1</sub><br>(Address Bit 1)                  | Н                              | 8                 | 32    | Input, active High. With $A_0$ , $A_2$ , and $A_3$ , addresses FIO internal registers.                                                |

| A <sub>2</sub><br>(Address Bit 2)                  | I                              | 9                 | 31    | Input, active High. With $A_0$ , $A_1$ , and $A_3$ , addresses FIO internal registers.                                                |

| A <sub>3</sub><br>(Address Bit 3)                  | 1                              | 10                | 30    | Input, active High. With $A_0,\ A_1,\ \mbox{and}\ A_2,\ \mbox{addresses}$ FIO internal registers.                                     |

Table 3. Signal/Pin Descriptions (Continued)

### Non-Z-BUS Mode

| Pin<br>Signals                           | Pin<br>Names                   | Pin Nu<br>Po |       | Signal<br>Description                                                                                                                |

|------------------------------------------|--------------------------------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> -D <sub>7</sub><br>(Data) | D <sub>0</sub> -D <sub>7</sub> | 11-18        | 29-22 | Bidirectional data bus.                                                                                                              |

| REQ/WT<br>(Request/Wait)                 | A                              | 1            | 39    | Output, active Low, REQUEST (ready) line for DMA transfer; WAIT line (open-drain) output for synchronized CPU and FIO data transfer. |

| DACK (DMA Acknowledge)                   | В                              | 2            | 38    | Input, active Low. DMA acknowledge.                                                                                                  |

| RD<br>(Read)                             | С                              | 3            | 37    | Input, active Low. Signals CPU read from FIO.                                                                                        |

| WR<br>(Write)                            | D                              | 4            | 36    | Input, active Low. Signals CPU write to FIO.                                                                                         |

| CE<br>(Chip Select)                      | E                              | 5            | 35    | Input, active Low. Used to select FIO.                                                                                               |

| $C/\overline{D}$<br>(Control/Data)       | F                              | 6            | 34    | Input, active High. Identifies control byte on $D_0$ - $D_7$ ; active Low identifies data byte on $D_0$ - $D_7$ .                    |

| INTACK<br>(Interrupt<br>Acknowledge)     | G                              | 7            | 33    | Input, active Low. Acknowledges an interrupt.                                                                                        |

| IEO<br>(Interrupt<br>Enable Out)         | Н                              | 8            | 32    | Output, active High. Sends interrupt enable to lower priority device IEI pin.                                                        |

| IEI<br>(Interrupt<br>Enable In)          | I                              | 9            | 31    | Input, active High. Receives interrupt enable from higher priority device IEO signal.                                                |

| INT<br>(Interrupt)                       | 1                              | 10           | 30    | Output, open drain, active Low. Signals FIO interrupt to CPU.                                                                        |

Table 3. Signal/Pin Descriptions (Continued)

Port 2-I/O Port Mode

| Pin<br>Signals                                | Pin<br>Names                   | Pin<br>Numbers | Mode                    | Signal<br>Description                                                                                                                                                                             |

|-----------------------------------------------|--------------------------------|----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub> -D <sub>7</sub><br>(Data)      | D <sub>0</sub> -D <sub>7</sub> | 29-22          | 2-Wire HS*<br>3-Wire HS | Bidirectional data bus.                                                                                                                                                                           |

| RFD/DAV<br>(Ready for Data/Data<br>Available) | A                              | 39             | 2-Wire HS<br>3-Wire HS  | Output, RFD active High. Signals peripherals that FIC is ready to receive data. DAV active Low signals that FIO is ready to send data to peripherals.                                             |

| ACKIN<br>(Acknowledge Input)                  | В                              | 38             | 2-Wire HS               | Input, active Low. Signals FIO that output data is received by peripherals or that input data is valid.                                                                                           |

| DAV/DAC<br>(Data Available/Data<br>Accepted)  | В                              | 38             | 3-Wire HS               | Input: DAV (active Low) signals that data is valid on bus. DAC (active High) signals that output data is accepted by peripherals.                                                                 |

| FULL                                          | С                              | 37             | 2-Wire HS               | Output, open drain, active High. Signals that FIO buffer is full.                                                                                                                                 |

| DAC/RFD<br>(Data Accepted/Read<br>for Data)   | C<br>y                         | 37             | 3-Wire HS               | Direction controlled by internal programming. Both active High. DAC (an output) signals that FIO has received data from peripheral; RFD (an input) signals that the listeners are ready for data. |

| EMPTY                                         | D                              | 36             | 2-Wire HS<br>3-Wire HS  | Output, open drain, active High. Signals that FIFO buffer is empty.                                                                                                                               |

| CLEAR                                         | E                              | 35             | 2-Wire HS<br>3-Wire HS  | Programmable input or output, active Low. Clears all data from FIFO buffer.                                                                                                                       |

| DATA DIR<br>(Data Direction)                  | F                              | 34             | 2-Wire HS<br>3-Wire HS  | Programmable input or output. Active High signals data input to Port 2; Low signals data output from Port 2.                                                                                      |

| IN <sub>0</sub>                               | G                              | 33             | 2-Wire HS<br>3-Wire HS  | Input line to $D_0$ of Control Register 3.                                                                                                                                                        |

| OUT1                                          | Н                              | 32             | 2-Wire HS<br>3-Wire HS  | Output line from $D_1$ of Control Register 3.                                                                                                                                                     |

| OE<br>(Output Enable)                         | I                              | 31             | 2-Wire HS<br>3-Wire HS  | Input, active Low. When Low, enables bus drivers.<br>When High, floats bus drivers at high impedance.                                                                                             |

| OUT <sub>3</sub>                              | 1                              | 30             | 2-Wire HS<br>3-Wire HS  | Output line from D <sub>3</sub> of Control register 3.                                                                                                                                            |

<sup>\*</sup>Handshake

Table 3. Signal/Pin Descriptions (Continued)

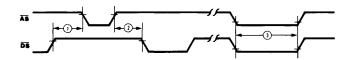

#### Reset

The FIO can be reset under either hardware or software control by one of the following methods:

- By forcing both AS and DS Low simultaneously in Z-BUS mode (normally illegal).

- By forcing RD and WR Low simultaneously in non-Z-BUS mode.

- By writing a 1 to the Reset bit in Control register 0 for software reset.

In the Reset state, all control bits are cleared to 0. Only after clearing the Reset bit (by

writing a 0 to it) can the other command bits be programmed. This action is true for both sides of the FIO when programmed as a CPU interface.

For proper system control, when Port 1 is reset, Port 2 is also reset. In addition, all Port 2's outputs are floating and all inputs are ignored. To initiate the data transfer, Port 2 must be enabled by Port 1. The Port 2 CPU can determine when it is enabled by reading Control register 0, which reads "floating" data bus if not enabled and "01H" if enabled.

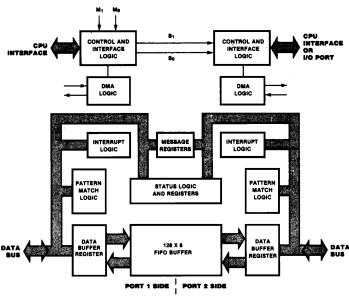

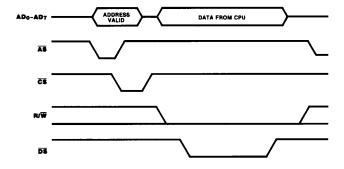

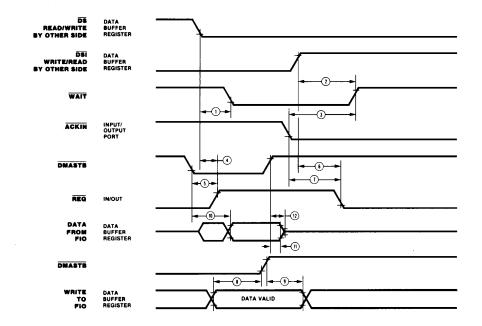

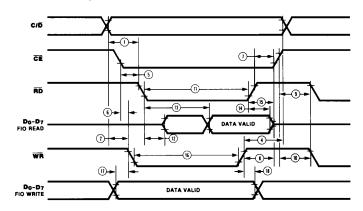

#### **CPU** Interfaces

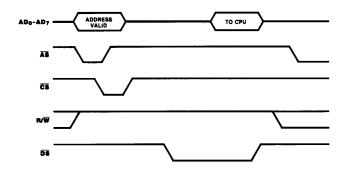

The FIO is designed to work with both Z-BUS- and non-Z-BUS-type CPUs on both Port 1 and Port 2. The Z-BUS configuration interfaces CPUs with time-multiplexed address and data information on the same pins. The Z8001, Z8002, and Z8 are examples of this type of CPU. The  $\overline{\rm AS}$  (Address Strobe) pin is used to latch the address and chip select information sent out by the CPU. The R/ $\overline{\rm W}$  (Read/Write) pin and the  $\overline{\rm DS}$  (Data Strobe) pin are used for timing reads and writes from the CPU to

the FIO (Figures 6 and 7).

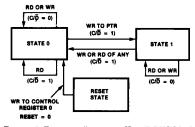

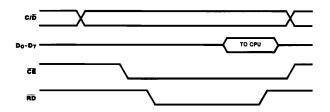

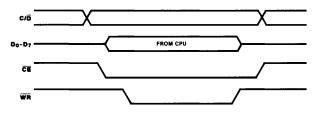

The non-Z-BUS configuration is used for CPUs where the address and data buses are separate. Examples of this type of CPU are the Z80 and 8080. The  $\overline{\text{RD}}$  (Read) and  $\overline{\text{WR}}$  (Write) pins are used to time reads and writes from the CPU to the FIO (Figures 9 and 10). The  $C/\overline{\text{D}}$  (Control/Data) pin is used to directly access the FIFO buffer ( $C/\overline{\text{D}}=0$ ) and to access the other registers ( $C/\overline{\text{D}}=1$ ). Read and write to all

Figure 6. Z-BUS Read Cycle Timing

Figure 7. Z-BUS Write Cycle Timing

#### **CPU Interface** (Continued)

registers except the FIFO buffer  $^{1}$  are two-step operations, described as follows (Figure 8). First, write the address ( $C/\overline{D}=1$ ) of the register to be accessed into the Pointer Register (State 0); second, read or write ( $C/\overline{D}=1$ ) to the register pointed at previously (State 1). Continuous status monitoring can be performed in State 1 by continuous Control Read operations ( $C/\overline{D}=1$ ).

<sup>1</sup>The FIFO buffer can also be accessed by this two-step operation.

Figure 8. Register Access in Non-Z-BUS Mode

Figure 9. Non-Z-BUS Read Cycle Timing

Figure 10. Non-Z-BUS Write Cycle Timing

#### WAIT Operation

When data is output by the CPU, the REQ/WT (WAIT) pin is active (Low) only when the FIFO buffer is full, the chip is selected, and the FIFO buffer is addressed. WAIT goes inactive when the FIFO buffer is not full.

When data is input by the CPU, the  $\overline{\text{REQ}/\text{WT}}$  pin becomes active (Low) only when the FIFO buffer is empty, the chip is selected, and the FIFO buffer is addressed. WAIT goes inactive when the FIFO buffer is not empty.

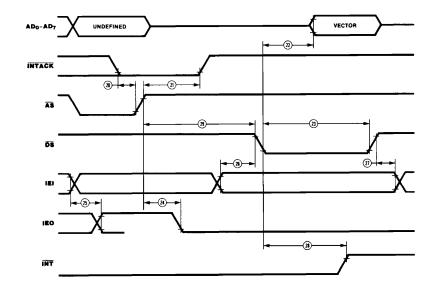

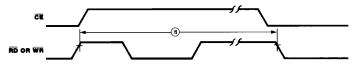

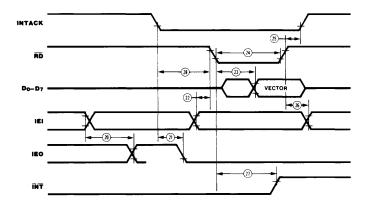

#### Interrupt Operation

The FIO supports the prioritized daisy chain interrupt protocol for both Z-BUS and non-Z-BUS operating modes (for more details refer to the Z-BUS Summary).

Each side of the FIO has seven sources of interrupt. The priorities of these devices are fixed in the following order (highest to lowest): Mailbox Message, Change in Data Direction, Pattern Match, Status Match, Overflow/ Underflow Error, Buffer Full, and Buffer Empty. Each interrupt source has three bits that control how it generates the interrupt. These bits are Interrupt Pending (IP), Interrupt Enable (IE), and Interrupt Under Service (IUS).

In addition, each side of the FIO has an interrupt vector and four bits controlling the FIO interrupt logic. These bits are Vector Includes Status (VIS), Master Interrupt Enable (MIE), Disable Lower Chain (DLC), and No

Vector (NV).

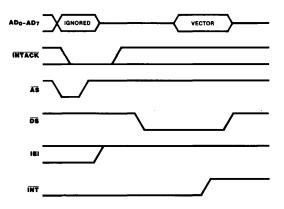

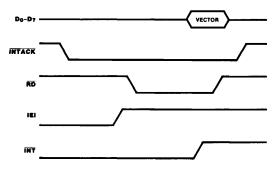

A typical Interrupt Acknowledge cycle for Z-BUS operation is shown in Figure 11 and for non-Z-BUS operation in Figure 12. The only difference is that in Z-BUS mode, INTACK is latched by AS, and in non-Z-BUS mode INTACK is not latched.

When MIE = 1, reading the vector always includes status, independent of the state of the VIS bit. In this way, when VIS = 0, all information can be obtained with one additional read, thus conserving vector space. When MIE = 0, reading the vector register returns the unmodified base vector so that it can be verified.

In non-Z-BUS mode, IPs do not get set while in State 1. Therefore, in order to minimize interrupt latency, the FIO should be left in State 0.

Figure 11. Z-BUS Interrupt Acknowledge Cycle

#### Interrupt Operation (Continued)

Figure 12. Non-Z-BUS Interrupt Acknowledge Cycle

#### **CPU to CPU Operation**

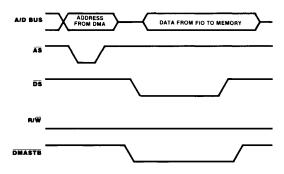

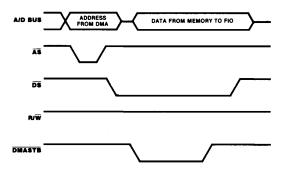

**DMA Operation.** The FIO is particularly well suited to work with a DMA in both Z-BUS and non-Z-BUS modes. A data transfer between the FIO and system memory can take place during every machine cycle on both sides of the FIO simultaneously.

In Z-BUS mode, the  $\overline{\text{DMASTB}}$  pin (DMA Strobe) is used to read or write into the FIFO buffer. The  $R/\overline{W}$  (Read/Write) and  $\overline{\text{DS}}$  (Data Strobe) signals are ignored by the FIO;

however, the  $\overline{CS}$  (Chip Select) signal is not ignored and therefore must be kept invalid. Figures 13 and 14 show typical timing.

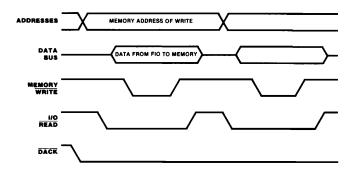

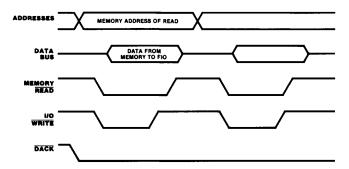

In Non-Z-BUS mode, the  $\overline{\rm DACK}$  pin (DMA Acknowledge) is used to tell the FIO that its DMA request is granted. After  $\overline{\rm DACK}$  goes Low, every read or write to the FIO goes into the FIFO buffer. Figures 15 and 16 show typical timing.

Figure 13. Z-BUS FIO to Memory Data Transaction

Figure 14. Z-BUS Memory to FIO Data Transaction

Figure 15. Non-Z-BUS FIO to Memory Transaction

Figure 16. Non-Z-BUS Memory to FIO Data Transaction

225

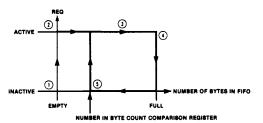

The FIO provides a special mode to enhance its DMA transfer capability. When data is written into the FIFO buffer, the REQ/WT (REQUEST) pin is active (Low) until the FIFO buffer is full. It then goes inactive and stays inactive until the number of bytes in the FIFO buffer is equal to the value programmed into the Byte Count Comparison register. Then the REQUEST signal goes active and the sequence starts over again (Figure 17).

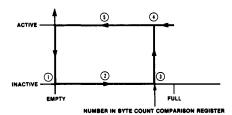

When data is read from the FIO, the REQ/WT pin (REQUEST) is inactive until the number of bytes in the FIFO buffer is equal to the value programmed in the Byte Count Comparison register. The REQUEST signal then goes active and stays active until the FIFO buffer is empty. When empty, REQUEST goes inactive and the sequence starts over again (Figure 18).

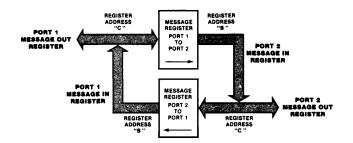

Message Registers. Two CPUs can communicate through a dedicated "mailbox" register without involving the 128  $\times$  8 bit FIFO buffer (Figure 19). This mailbox approach is useful for transferring control parameters between the interfacing devices on either side of the FIO without using the FIFO buffer. For example, when Port 1's CPU writes to the Message Out register, Port 2's message IP is set. If interrupts are enabled, Port 2's CPU is interrupted. Port 2's message IP status is readable from the Port 1 side. When Port 2's CPU reads the data from its Message In register, the Port 2 IP is cleared. Thus, Port 1's CPU can read when the message has been read and can now send another message or follow whatever protocol that is set up between the two CPU's. The same transfer can also be made from Port 2's CPU to Port 1's CPU.

#### NOTES

- 1. FIFO empty.

- 2. REQUEST enabled, FIO requests DMA transfer.

- 3. DMA transfers data into the FIO.

- 4. FIFO full, REQUEST inactive.

- The FIFO empties from the opposite port until the number of bytes in the FIFO buffer is the same as the number programmed in the Byte Count Comparison register.

Figure 17. Byte Count Control: Write to FIO

#### NOTES:

- 1. FIFO empty.

- 2. CPU/DMA fills FIFO buffer from the opposite port.

- Number of bytes in FIFO buffer is the same as the number of bytes programmed in the Byte Count Comparison register.

- REQUEST goes active.

DMA transfers data out of FIFO until it is empty.

Figure 18. Byte Count Control: Read from FIO

CLEAR (Empty) FIFO Operation. The CLEAR FIFO bit (active Low) clears the FIFO buffer of data. Writing a 0 to this bit empties the FIFO buffer, inactivates the REQUEST line, and disables the handshake (if programmed). The CLEAR bit does not affect any control or data register. To remove the CLEAR state, write a 1 to the CLEAR bit.

In CPU/CPU mode, under program control, only one of the ports can empty the FIFO by writing to its Control Register 3, bit 6. The Port 1 CPU must program bit 7 in Control Register 3 to determine which port controls the CLEAR FIFO operation (0 = Port 1 control; 1 = Port 2 control).

Direction of Data Transfer Operation. The Data Direction bit controls the direction of data transfer in the FIFO buffer. The Data Direction bit is defined as 0 = output from CPU and 1 = input to CPU. This bit reads correctly when read by either port's CPU. For example, if Port 1's CPU reads a 0 (CPU output) in its Data Direction bit, then Port 2's CPU reads a 1 (input to CPU) in its Data Direction bit.

In CPU/CPU mode, under program control, only one of the ports can control the direction of data transfer. The Port 1 CPU must program bit 5 in Control Register 3 to determine which port controls the data direction (0 = Port 1 control; 1 = Port 2 control). Figure 20 shows FIO data transfer options.

NOTE: Usable only for CPU/CPU interface.

Figure 19. Message Register Operation

Figure 20. FIO Data Transfert Options

#### CPU to I/O Operation

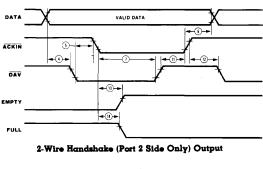

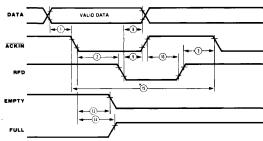

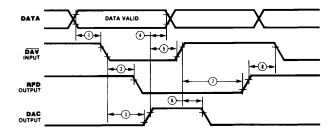

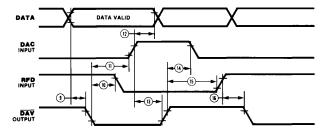

When Port 2 is programmed in the Interlocked 2-Wire Handshake mode or the 3-Wire Handshake mode, and Port A is programmed in Z-BUS or non-Z-BUS Microprocessor mode, the FIO interfaces a CPU and a peripheral device. In the Interlocked 2-Wire Handshake mode, RFD/ $\overline{\rm DAV}$  and  $\overline{\rm ACKIN}$  strobe data to and from Port 2. In the 3-Wire Handshake mode, RFD/ $\overline{\rm DAV}$ ,  $\overline{\rm DAV}$ /DAC, and DAC/RFD signals control data flow.

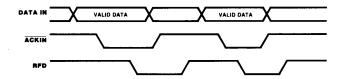

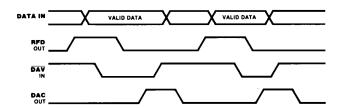

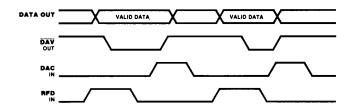

Interlocked 2-Wire Handshake. In the Interlocked Handshake, the action of the FIO must be acknowledged by the other half of the handshake before the next action can take place. In output mode, Port 2 does not indicate that new data is available until the external device indicates it is ready for the data. Similarly, in input mode, Port 2 does not indicate that it is ready for new data until the data source indicates that the previous byte of the data is no longer available, thereby acknowledging Port 2's acceptance of the last byte. This allows the FIO to directly interface to a Z8's port, a CIO's port, a UPC's port, another FIO port, or another FIFO Z8060, with no external logic (Figures 21 and 22).

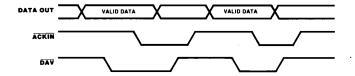

3-Wire Handshake. The 3-Wire Handshake is designed for applications in which one output port is communicating with many input ports simultaneously. It is essentially the same as the Interlocked Handshake, except that two signals are used to indicate that an input port is ready for new data or that it has accepted the present data. In the 3-Wire Handshake, the rising edge of the RFD status line indicates that the port is ready for data, and the rising edge of the DAC status line indicates that the data has been accepted. With 3-Wire Handshake, the lines of many input ports can be bussed together with open-drain drivers and the out-

put port knows when all of the ports are ready and have accepted the data. This handshake is the same handshake used in the IEEE-488 Instruments. Since the port's direction can be changed under software control, bidirectional IEEE-488-type transfers can be performed. Figures 23 and 24 show the timings associated with 3-Wire Handshake communications.

**CLEAR FIFO Operation.** In CPU-to-I/O operation, the CLEAR FIFO operation can be performed by the CPU side (Port 1) under software control as previously explained. The CLEAR FIFO operation can also be performed under hardware control by defining the  $\overline{\text{CLEAR}}$  pin of Port 2 as an input (Control Register 3, bit 7 = 1).

For cascading purposes, the  $\overline{\text{CLEAR}}$  pin can also be defined as an output (Control Register 3, bit 7 = 0), which reflects the current state of the  $\overline{\text{CLEAR}}$  FIFO bit. It can then empty other FIOs or initialize other devices in the system.

**Data Direction Control.** In CPU-to-I/O mode, the direction of data transfer can be controlled by the CPU side (Port 1) under software control as previously explained. The data direction can also be determined by hardware control by defining the Data Direction pin of Port 2 as an input (Control Register 3, bit 5 = 1).

For cascading purposes, the Data Direction pin can also be defined as an output (Control Register 3, bit  $5\,=\,0$ ) pin which reflects the current state of the Data Direction bit. It can then be used to control the direction of data transfer for other FIOs or for external logic.

On the Port 2 side, when data direction is 0, Port 2 is in Output Handshake mode. When data direction is 1, Port 2 is in Input Handshake mode.

Figure 21. Interlocked Handshake Timing (Imput) Port 2 Side Only

Figure 22. Interlocked Handshake Timing (Output) Port 2 Side Only

Figure 23. Input (Acceptor) Timing IEEE-488 Port: Port 2 Side Only

Figure 24. Output (Source) Timing IEEE-488 HS Port: Port 2 Side Only

#### Programming

The programming of the FIO is greatly simplified by the efficient grouping of the various operation modes in the control registers. Since all of the control registers are read/write, the need for maintaining their image in system memory is eliminated. Also, the read/write feature of the registers aids in system debugging.

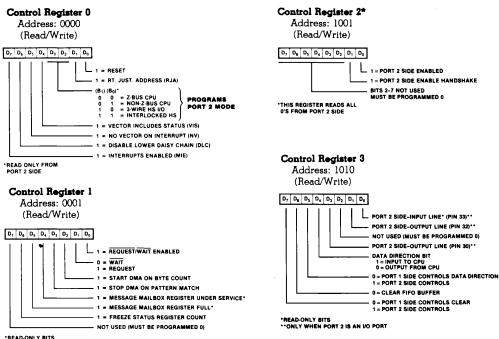

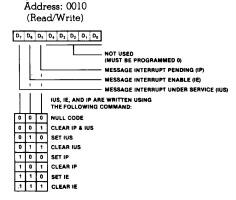

Each side of the FIO has 16 registers. All 16 registers are used by the Port 1 side; Control register 2 is not used on the Port 2 side. All registers are addressable 0<sub>H</sub> through F<sub>H</sub>.

In the Z-BUS Low Byte mode, the FIO allows two methods for register addressing under control of the Right Justify Address (RJA) bit in Control register 0. When RJA = 0, address bus bits 1-4 are used for register addressing and bits 5, 6, and 7 are ignored (Table 4). When RJA = 1, bits 0-3 are used for the

register addresses, and bits 4-7 are ignored.

**Control Registers.** These four registers specify FIO operation. The Port 2 side control registers operate only if the Port 2 device is a CPU. The Port 2 CPU can control interface operations, including data direction, only when enabled by the setting of bit 0 in the Port 1 side of Control Register 2. A 1 in bit 1 of the same register enables the handshake logic.

**Interrupt Status Registers.** These four registers control and monitor the priority interrupt functions for the FIO.

**Interrupt Vector Register.** This register stores the interrupt service routine address. This vector is placed on  $D_0$ – $D_7$  when IUS is set by the Interrupt Acknowledge signal from the CPU. When bit 4 (Vector Includes Status) is set in Control Register 0, the reason for the interrupt

| Non Z-BUS                         | D7-D4                                                                | $D_3$                              | D <sub>2</sub>                     | $D_1$                              | $D_0$                              |                 |

|-----------------------------------|----------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-----------------|

| Z-BUS High                        |                                                                      | A <sub>3</sub>                     | A <sub>2</sub>                     | A <sub>1</sub>                     | A <sub>0</sub>                     |                 |

| Z-BUS Low RJA=0                   | AD <sub>7</sub> -AD <sub>5</sub><br>AD <sub>7</sub> -AD <sub>4</sub> | AD <sub>4</sub><br>AD <sub>3</sub> | AD <sub>3</sub><br>AD <sub>2</sub> | AD <sub>2</sub><br>AD <sub>1</sub> | AD <sub>1</sub><br>AD <sub>0</sub> | AD <sub>0</sub> |

| Description                       |                                                                      |                                    |                                    |                                    |                                    |                 |

| Control Register 0                | x                                                                    | 0                                  | 0                                  | 0                                  | 0                                  | x               |

| Control Register 1                | x                                                                    | 0                                  | 0                                  | 0                                  | 1                                  | x               |

| Interrupt Status Register 0       | x                                                                    | 0                                  | 0                                  | 1                                  | 0                                  | x               |

| Interrupt Status Register 1       | x                                                                    | 0                                  | 0                                  | 1                                  | 1                                  | x               |

| Interrupt Status Register 2       | x                                                                    | 0                                  | 1                                  | 0                                  | 0                                  | x               |

| Interrupt Status Register 3       | x                                                                    | 0                                  | 1                                  | 0                                  | 1                                  | x               |

| Interrupt Vector Register         | x                                                                    | 0                                  | 1                                  | 1                                  | 0                                  | x               |

| Byte Count Register               | x                                                                    | 0                                  | l                                  | 1                                  | 1                                  | x               |

| Byte Count Comparison<br>Register | x                                                                    | l                                  | 0                                  | 0                                  | 0                                  | x               |

| Control Register 2*               | x                                                                    | l                                  | 0                                  | 0                                  | 1                                  | x               |

| Control Register 3                | x                                                                    | 1                                  | 0                                  | 1                                  | 0                                  | x               |

| Message Out Register              | x                                                                    | l                                  | 0                                  | 1                                  | 1                                  | x               |

| Message In Register               | x                                                                    | 1                                  | 1                                  | 0                                  | 0                                  | x               |

| Pattern Match Register            | x                                                                    | 1                                  | 1                                  | 0 -                                | 1                                  | x               |

| Pattern Mask Register             | x                                                                    | 1                                  | 1                                  | 1                                  | 0                                  | , x             |

| Data Buffer Register              | x                                                                    | l                                  | 1                                  | 1                                  | 1                                  | x               |

x = Don't Care

Table 4. FIO Register Address Summary

<sup>\*</sup>Register is only on Port 1 side

### **Programming** Continued)

is encoded within the vector address in bits 1, 2, and 3. If bit 5 is set in Control register 0, no vector is output by the FIO during an Interrupt Acknowledge cycle. However, IUS is set as usual.

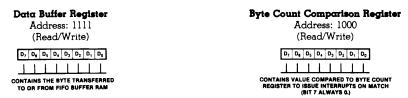

Byte Count Compare Register. This register contains a value compared with the byte count in the Byte Count register. If the Byte Count Compare interrupt is enabled, an interrupt will occur upon compare.

Message Out Register. Either CPU can place a message in its Message Out register. If the opposite side Message register interrupt is enabled, the receiving side CPU will receive an interrupt request, advising that a message is present in its Message In register. Bit 5 in Control Register 1 on the initiating side is set when a message is written. It is cleared when the message is read by the receiving CPU.

**Message In Register.** This register receives a message placed in the Message Out register by the opposite side CPU.

Pattern Match Register. This register contains a bit pattern matched against the byte in the Data Buffer register. When these patterns match, a Pattern Match interrupt will be generated, if previously enabled.

Pattern Mask Register. The Pattern Mask register may be programmed with a bit pattern mask that limits comparable bits in the Pattern Match register to non-masked bits (1 = mask).

**Data Buffer Register.** This register contains the data to be read from or written to the FIFO buffer.

Byte Count Register. This is a read-only register, containing the byte count for the FIFO buffer. The byte count is derived by subtracting the number of bytes read from the buffer from the number of bytes written into the buffer. The count is "frozen" for an accurate reading by setting bit 6 (Freeze Status register) in Control Register 1. This bit is cleared when the Byte Count register read is completed.

Figure 25. Typical Application: Node Controller

## Registers

Figure 26. Control Registers

Interrupt Status Register 0

Figure 27. Interrupt Status Registers

#### Registers (Continued)

#### Interrupt Status Register 1 Address: 0011 (Read/Write) D7 D6 D5 D4 D3 D2 D, D0 DATA DIRECTION CHANGE INTERRUPT = PATTERN MATCH FLAG **UNDER SERVICE (IUS)** PATTERN MATCH INTERRUPT PENDING (IP) DATA DIRECTION CHANGE INTERRUPT PATTERN MATCH INTERRUPT ENABLED (IE) ENABLE (IE) PATTERN MATCH INTERRUPT DATA DIRECTION CHANGE INTERRUPT UNDER SERVICE (IUS) PENDING (IP) IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: NOT USED (MUST BE PROGRAMMED 0) IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: NULL CODE 0 0 0 CLEAR IP & IUS 0 0 1 0 0 0 NULL CODE SET IUS 0 1 0 0 0 1 CLEAR IP & IUS CLEAR IUS 0 1 1 0 1 0 SET IUS SET IP 1 0 0 0 1 1 CLEAR IUS CLEAR IP 1 0 1 1 0 0 SET IP SET IE 1 1 0 1 0 1 CLEAR IP **Interrupt Status Register 2** CLEAR IE 1 1 1 0 SET IE Address: 0100 1 1 1 CLEAR IE (Read/Write) \*READ-ONLY BITS D, D6 D5 D4 D3 D2 D, D0 BYTE COUNT COMPARE INTERRUPT UNDERFLOW ERROR\* UNDER SERVICE (IUS) ERROR INTERRUPT PENDING (ID) BYTE COUNT COMPARE INTERRUPT ERROR INTERRUPT ENABLED (IE) ENABLE (IE) ERROR INTERRUPT UNDER SERVICE (IUS) BYTE COUNT COMPARE INTERRUPT OVERFLOW ERROR\* IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND NULL CODE 0 0 0 0 0 0 NULL CODE CLEAR IP & IUS 0 0 0 1 CLEAR IP & IUS 0 1 SET IUS 0 1 0 0 1 0 SET IUS CLEAR IUS 0 1 1 CLEAR IUS 0 1 1 **Interrupt Status Register 3** SET IP 1 0 0 1 0 0 SET IP CLEAR IP 0 1 0 1 CLEAR IP Address: 0101 1 1 SET IE 1 0 1 1 0 SET IE (Read/Write) CLEAR IE 1 1 1 1 CLEAR IE 1 1 D, D, D, D, D, D, D, D, \*READ-ONLY BITS FULL INTERRUPT UNDER SERVICE (IUS) FULL INTERRUPT ENABLE (IE) EMPTY INTERRUPT PENDING (IP) FULL INTERRUPT PENDING (IP) EMPTY INTERRUPT ENARGE (IF) EMPTY INTERRUPT UNDER SERVICE (IUS) IUS, IE, AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: . BUFFER FULL\* NULL CODE 0 0 0 ILIS IF AND IP ARE WRITTEN USING THE FOLLOWING COMMAND: CLEAR IP & IUS 0 0 000 NULL CODE SET IUS 0 1 0 CLEAR IP & IUS CLEAR IUS 0 1 1 0 0 1 SET IP 1 0 0 0 1 0 SET IUS CLEAR IUS 0 1 1 CLEAR IP 10 1 1 1 0 1 0 0 SET IP SET IE 0 1 CLEAR IP CLEAR IE 1 1 1 0 SET IE 1

Figure 27. Interrupt Status Registers (Continued)

1 1 1

\*READ-ONLY BITS

CLEAR IE

#### Registers (Continued) **Byte Count Register** Interrupt Vector Register Address: 0111 Address: 0110 (Read/Write) D<sub>7</sub> D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> D7 D6 D5 D4 D3 D2 D1 D0 NO INTERRUPTS PENDING 0 0 0 BUFFER EMPTY 0 Figure 28. Byte Count Register BUFFER FULL 0 1 OVER/UNDERFLOW ERROR 0 1 VECTOR STATUS BYTE COUNT MATCH PATTERN MATCH DATA DIRECTION CHANGE MAILBOX MESSAGE 1

Figure 29. Interrupt Vector Register

Figure 31. Pattern Mask Register

Figure 32. Data Buffer Registe Figure 33. Byte Count Comparison Register

| Message Out Register Address: 1011 (Read/Write)                                                                                                                                                           | Message In Register<br>Address: 1100<br>(Read Only)                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>5</sub> D <sub>2</sub> D <sub>7</sub> D <sub>0</sub> D <sub>0</sub> STORES MESSAGE SENT TO MESSAGE IN REGISTER ON OPPOSITE PORT OF FIO | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>6</sub> D <sub>3</sub> D <sub>2</sub> D, D <sub>0</sub> STORES MESSAGE RECEIVED FROM MESSAGE OUT REGISTER ON OPPOSITE PORT OF CPU |

Figure 34. Message Out Register

Figure 35. Message In Register

235

### **Absolute Maximum Ratings**

| Voltages on all inputs and outputs   |

|--------------------------------------|

| with respect to GND0.3 V to $+7.0$ V |

| Operating Ambient                    |

| Temperature0°C to +70°C              |

| Storage Temperature65 °C to +150 °C  |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

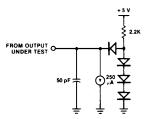

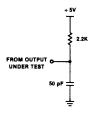

#### Standard Test Conditions

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the referenced pin. Standard conditions are as follows:

Figure 36. Standard Test Load

- $\blacksquare$  +4.75 V  $\leq$  V<sub>CC</sub>  $\leq$  +5.25 V

- GND = 0 V

- T<sub>A</sub> as specified in Ordering Information

Figure 37. Open-Drain Test Load

#### DC Characteristics

| Symbol          | Parameter                                   | Min    | Max                   | Unit | Condition                   |

|-----------------|---------------------------------------------|--------|-----------------------|------|-----------------------------|

| $v_{IH}$        | Input High Voltage                          | 2.0    | V <sub>CC</sub> + 0.3 | v    |                             |

| $V_{IL}$        | Input Low Voltage                           | -0.3   | 0.8                   | V    |                             |

| $v_{OH}$        | Output High Voltage                         | 2.4    |                       | V    | $I_{OH} = -250 \mu A$       |

| $v_{ol}$        | Output Low Voltage                          |        | 0.4                   | V    | $I_{OL} = +2.0 \text{ mA}$  |

|                 |                                             |        | 0.5                   | V    | $I_{OL} = +3.2 \text{ mA}$  |

| $I_{IL}$        | Input Leakage                               | -10.0  | +10.0                 | μΑ   | $0.4 \le V_{IN} \le +2.4V$  |

| $I_{OL}$        | Output Leakage                              | - 10.0 | +10.0                 | μΑ   | $0.4 \le V_{OUT} \le +2.4V$ |

| $I_{LM}$        | Mode Pins Input Leakage<br>(Pins 19 and 21) | -100   | +10.0                 | μA   | $0 < V_{IN} < V_{CC}$       |

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current              |        | 200                   | mA   |                             |

$V_{CC}$  = 5 V ± 5% unless otherwise specified, over specified temperature range.

### Capacitance

| Symbol          | Parameter                 | Min | Max | Unit | Test Condition     |

|-----------------|---------------------------|-----|-----|------|--------------------|

| C <sub>IN</sub> | Input Capacitance         |     | 10  | рF   |                    |

| $C_{OUT}$       | Output Capacitance        |     | 15  | рF   | Unmeasured Pins    |

| $C_{I/O}$       | Bidirectional Capacitance |     | 20  | рF   | Returned to Ground |

| Inputs          |                           |     |     |      |                    |

| tr              | Any Input Rise Time       |     | 100 | ns   |                    |

| tf              | Any Input Fall Time       |     | 100 | ns   |                    |

f = 1 MHz, over specified temperature range.

## **Z-BUS CPU Inteface Timing**

| No.  | Symbol         | Parameter                                                                                                            | 4:<br>Min | MHz<br>Max | 6 I<br>Min  | MHz<br>Max | Notes*†  |

|------|----------------|----------------------------------------------------------------------------------------------------------------------|-----------|------------|-------------|------------|----------|

|      | _ <del>-</del> |                                                                                                                      |           | 1-144      |             |            | 210100 1 |

| 1    | TwAS           | AS Low Width                                                                                                         | 70        |            | 50          |            | 1        |

| 2    | TsA(AS)        | Address to AS † Setup Time                                                                                           | 30        |            | 10          |            | 1        |

| 3    | ThA(AS)        | Address to AS † Hold Time                                                                                            | 50        |            | 30          |            | 1        |

| 4    | TsCSO(AS)      | CS to AS † Setup Time                                                                                                | 0         |            | 0           |            | 1        |

| 5 -  | - ThCSO(AS) -  | — CS to AS † Hold Time —————                                                                                         | 60 -      |            | —— 40 —     |            | —— 1 —   |

| 6    | TdAS(DS)       | $\overline{\mathrm{AS}}$ † to $\overline{\mathrm{DS}}$ † Delay                                                       | 60        |            | 40          |            | 1        |

| 7    | TsA(DS)        | Address to $\overline{DS} \downarrow$ (with $\overline{AS} \uparrow$ to $\overline{DS} \downarrow = 60 \text{ ns}$ ) | 120       |            | 100         |            |          |

| 8    | TsRWR(DS)      | $R/\overline{W}$ (Read) to $\overline{DS} \downarrow S$ etup Time                                                    | 100       |            | 80          |            |          |

| 9    | TsRWW(DS)      | R/W (Write) to DS ↓ Setup Time                                                                                       | 0         |            | 0           |            |          |

| 10 - | - TwDS         | — DS Low Width —                                                                                                     | 390 -     |            | <del></del> |            |          |

| 11   | TsDW(DSf)      | Write Data to DS ↓ Setup Time                                                                                        | 30        |            | 20          |            |          |

| 12   | TdDS(DRV)      | DS (Read)   to Address Data Bus Driven                                                                               | 0         |            | 0           |            |          |

| 13   | TdDSf(DR)      | DS I to Read Data Valid Delay                                                                                        |           | 250        |             | 180        |          |

| 14   | ThDW(DS)       | Write Data to DS † Hold Time                                                                                         | 30        |            | 20          |            |          |

| 15 - | - TdDSr(DR)    | — DS ↑ to Read Data Not Valid Delay ————                                                                             | 0 -       |            | o <b>_</b>  |            |          |

| 16   | TdDS(DRz)      | DS † to Read Data Float Delay                                                                                        |           | 70         |             | <b>4</b> 5 | 2        |

| 17   | ThRW(DS)       | $R/\overline{W}$ to $\overline{DS}$ † Hold Time                                                                      | 55        |            | 40          |            |          |

| 18   | TdDS(AS)       | DS ↑ to AS ↓ Delay                                                                                                   | 50        |            | 25          |            |          |

| 19   | Trc            | Valid Access Recovery Time                                                                                           | 1000      |            | 650         |            | 3        |

#### NOTES:

<sup>1.</sup> Parameter does not apply to Interrupt Acknowledge trans-

Float delay is measured to the time when the output has changed 0.5 V from steady state with minimum as load and load and maximum do load.

<sup>3.</sup> This is the delay from DS of one CIO access to DS of another FIO access (either read or write).

4. All timing references assume 2.0 V for a logic "1" and 0.8 V for a logic "0". All timings are preliminary and subject to change.

† Units in nanoseconds (ns).

## **Z-BUS CPU Inteface Timing (Continued)**

## Z-BUS CPU Interrupt Acknowledge Timing

|     |             |                                                         | 4   | MHz         | 6 1 | MHz             |         |

|-----|-------------|---------------------------------------------------------|-----|-------------|-----|-----------------|---------|

| No. | Symbol      | Parameter                                               | Min | Max         | Min | Max             | Notes*† |

| 20  | TsIA(AS)    | INTACK to AS † Setup Time                               | 0   |             |     | 0               |         |

| 21  | ThIA(AS)    | INTACK to AS † Hold Time                                | 250 |             | 250 |                 |         |

| 22  | TsDSA(DR)   | DS (Acknowledge)   to Read Data Valid Delay             |     | 250         |     | 180             |         |

| 23  | TwDSA       | DS (Acknowledge) Low Width                              | 390 |             | 250 |                 |         |

| 24- | -TdAS(IEO)- | — AS to IEO I Delay (INTACK Cycle)————                  |     | <del></del> |     | <del></del> 250 | 4       |

| 25  | TdIEI(IEO)  | IEI to IEO Delay                                        |     | 150         |     | 100             | 4       |

| 26  | TsIEI(DSA)  | IEI to DS (Acknowledge) ↓ Setup Time                    | 100 |             | 70  |                 |         |

| 27  | ThIEI(DSA)  | IEI to $\overline{\text{DS}}$ (Acknowledge) † Hold Time | 50  |             | 30  |                 | 4       |

| 28  | TdDS(INT)   | DS (INTACK Cycle) to INT Delay                          |     | 900         |     | 800             |         |

| 29  | TdDCST      | Interrupt Daisy Chain Settle Time                       |     |             |     |                 | 4       |

NOTES:

and TdIEI(IEO) for each peripheral, separating them in the chain.

\* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

NOTES:

4. The parameters for the devices in any particular daisy chain must meet the following constraint: The delay from AS to DS must be greater than the sum of TAGS(EO) for the highest priority peripheral, TsIEI(DSA) for the lowest priority peripheral

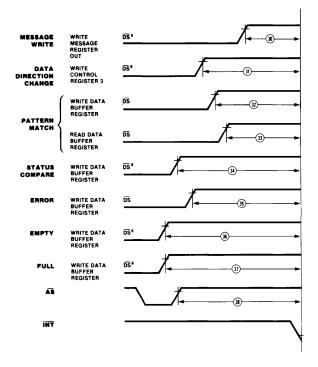

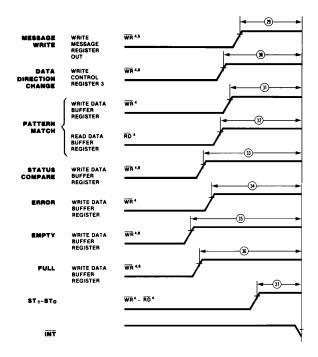

## **Z-BUS Interrupt Timing**

|     |            |                                         | 41          | MHz  | 61  | MHz |         |

|-----|------------|-----------------------------------------|-------------|------|-----|-----|---------|

| No. | Symbol     | Parameter                               | Min         | Max  | Min | Мах | Notes*† |

| 30  | TdMW(INT)  | Message Write to INT Delay              |             | 1    |     | 1   | 5       |

| 31  | TdDC(INT)  | Data Direction Change to INT Delay      |             | 1    |     | 1   | 6       |

| 32  | TdPMW(INT) | Pattern Match to INT Delay (Write Case) |             | 1    |     | 1   |         |

| 33  | TdPMR(INT) | Pattern Match (Read Case) to INT Delay  |             | 1    |     | 1   |         |

| 34  | -TdSC(INT) | Status Compare to INT Delay             | <del></del> | — 1— |     | -1  | 6       |

| 35  | TdER(INT)  | Error to INT Delay                      |             | 1    |     | 1   |         |

| 36  | TdEM(INT)  | Empty to INT Delay                      |             | 1    |     | 1   | 6       |

| 37  | TdFL(INT)  | Full to INT Delay                       |             | 1    |     | 1   | 6       |

| 38  | TdAS(INT)  | AS to INT Delay                         |             |      |     |     |         |

NOTES:

Write is from the other side of FIO.

Write can be from either side, depending on programming of FIO.

\* Timings are preliminary and subject to change.

† Units equal to AS Cycles + ns.

## **Z-BUS Request/Wait Timing**

|     |                               |                                 | 4     | MHz             | 6 1                       | MHz                   |         |

|-----|-------------------------------|---------------------------------|-------|-----------------|---------------------------|-----------------------|---------|

| No. | Symbol                        | Parameter                       | Min   | Max             | Min                       | Мах                   | Notes*† |

| 1   | TdDS(WAIT)                    | ĀS ↑ to WAIT ↓ Delay            |       | 190             |                           | 160                   |         |

| 2   | TdDS1(WAIT)                   | DSI t to WAIT t Delay           |       | 1000            |                           | 1000                  |         |

| 3   | TdACK(WAIT)                   | ACKIN I to WAIT 1 Delay         |       | 1000            |                           | 1000                  | 1       |

| 4   | TdDS(REQ)                     | - DS ↓ to REQ ↑ Delay —         |       | — <b>3</b> 50 — |                           | <b>—</b> 300 <b>—</b> |         |

| 5   | TdDMA(REQ)                    | DMASTB ↓ to REQ ↑ Delay         |       | 350             |                           | 300                   |         |

| 6   | TdDS1(REQ)                    | DSl 1 to REQ   Delay            |       | 1000            |                           | 1000                  |         |

| 7   | TdACK(REQ)                    | ACKIN ↓ to REQ ↓ Delay          |       | 1000            |                           | 1000                  |         |

| 8 – | <ul> <li>TdSU(DMA)</li> </ul> | – Data Setup Time to DMASTB ——— | 200 - |                 | <del></del> 150 <b></b> - |                       |         |

| 9   | TdH(DMA)                      | Data Hold Time to DMASTB        | 30    |                 | 20                        |                       |         |

| 10  | TdDMA(DR)                     | DMASTB ↓ to Valid Data          |       | 150             |                           | 100                   |         |

| 11  | TdDMA(DRH)                    | DMASTB 1 to Data Not Valid      | 0     |                 | 0                         |                       |         |

| 12  | TdDMA(DR2)                    | DMASTB † to Data Bus Float      |       | 70              |                           | 45                    |         |

NOTES:

1. The delay is from DAV for 3-Wire Input Handshake. The delay is from DAC for 3-Wire Handshake.

<sup>\*</sup> Timings are preliminary and subject to change. † Units in nanoseconds (ns).

### **Z-BUS Reset Timing**

|     |             |                                                                          | 4 MHz |     | 6 MHz |     |         |  |

|-----|-------------|--------------------------------------------------------------------------|-------|-----|-------|-----|---------|--|

| No. | Symbol      | Parameter                                                                | Min   | Max | Min   | Max | Notes*† |  |

| 1   | TdDSQ(AS)   | Delay from DS 1 to AS 1 for No Reset                                     | 40    |     | 20    |     |         |  |

| 2   | TdASQ(DS)   | Delay for $\overline{AS}$ 1 to $\overline{DS}$ 1 for No Reset            | 50    |     | 30    |     |         |  |

| 3   | Tw(AS + DS) | Minimum Width of $\overline{AS}$ and $\overline{DS}$ Both Low for Reset. | 500   |     | 350   |     | 1       |  |

NOTES:

- \* Timings are preliminary and subject to change. † Units in nanoseconds (ns).

### Non-Z-BUS CPU Interface Timing

|      |              |                                                                  | 41    | MHz | 6 1             | (Hz |         |

|------|--------------|------------------------------------------------------------------|-------|-----|-----------------|-----|---------|

| No.  | Symbol       | Parameter                                                        | Min   | Max | Min             | Max | Notes*† |

| 1    | TsA(RD)      | Address Setup to RD                                              | 80    |     | 80              |     | 1       |

| 2    | TsA(WR)      | Address Setup to WR ↓                                            | 80    |     | 80              |     |         |

| 3    | ThA(RD)      | Address Hold Time to RD †                                        | 0     |     | 0               |     | 1       |

| 4 —  | – ThA(WR) —— | — Address Hold Time to WR †————                                  | 0 -   |     | <del></del> 0 - |     |         |

| 5    | TsCEI(RD)    | CE Low Setup Time to RD                                          | . 0   |     | 0               |     | 1       |

| 6    | TsCEI(WR)    | $\overline{\text{CE}}$ Low Setup Time to $\overline{\text{WR}}$  | 0     |     | 0               |     |         |

| 7    | ThCEI(RD)    | CE Low Hold Time to RD                                           | 0     |     | 0               |     | 1       |

| 8 —  | -ThCEI(WR) - | — CE Low Hold Time to WR —                                       | 0_    |     | 0 -             |     |         |

| 9    | TsCEh(RD)    | $\overline{\text{CE}}$ High Setup Time to $\overline{\text{RD}}$ | 100   |     | 70              |     | 1       |

| 10   | TsCEh(WR)    | CE High Setup Time to WR                                         | 100   |     | 70              |     |         |

| 11   | TwRD1        | RD Low Width                                                     | 390   |     | 250             |     |         |

| 12 - | -TdRD(DRA) - | — RD ↓ to Read Data Active Delay ———                             | 0 -   |     | 0 -             |     |         |

| 13   | TdRDf(DR)    | RD ↓ to Valid Data Delay                                         |       | 250 |                 | 180 |         |

| 14   | TdRDr(DR)    | RD 1 to Read Data Not Valid Delay                                | 0     |     | 0               |     |         |

| 15   | TdRD(DRz)    | RD † to Data Bus Float                                           |       | 70  |                 | 45  | 2       |

| 16 - | -TwWR1       | ── WR Low Width ──                                               | 390 - |     | 250 -           |     |         |

| 17   | TsDW(WR)     | Data Setup Time to WR                                            | 0     |     | 0               |     |         |

| 18   | ThDW(WR)     | Data Hold Time to WR                                             | 30    |     | 20              |     |         |

| 19   | Trc          | Valid Access Recovery Time                                       | 1000  |     | 650             |     | 3       |

#### NOTES:

- 1. Parameter does not apply to Interrupt Acknowledge transactions.

- Froat delay is measured to the time the output has changed

O.5 V from steady state with minimum ac load and maximum dc load.

- 3. This is the delay from RD I to  $\overline{WR}$  I of one FIO access to  $\overline{RD}$  is or  $\overline{WR}$  I of another FIO access.

\* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

Internal circuitry allows for the reset provided by the Z8 (DS held Low while AS pulses) to be sufficient.

## Non-Z-BUS CPU Interface Timing(Continued)

Non-Z-BUS CPU Interface Timing

Non-Z-BUS Interface Timing

### Non-Z-BUS Interrupt Acknowledge Timing

|     |             |                                                        | 41             | MHz | 6 1             | MHz |         |

|-----|-------------|--------------------------------------------------------|----------------|-----|-----------------|-----|---------|

| No. | Symbol      | Parameter                                              | Min            | Max | Min             | Max | Notes†* |

| 20  | TdIEI(IEO)  | IEI to IEO Delay                                       |                | 150 |                 | 100 | 4       |

| 21  | TdI(IEO)    | INTACK ↓ to IEO ↓ Delay                                |                | 350 |                 | 250 | 4       |

| 22  | TsIEI(RDA)  | IEI Setup Time to $\overline{\text{RD}}$ (Acknowledge) | 100            |     | 70              |     | 4       |

| 23  | TdRD(DR)    | RD I to Vector Valid Delay                             |                | 250 |                 | 180 |         |

| 24- | —TwRD1(IA)— | Read Low Width (Interrupt Acknowledge)                 | <del>390</del> |     | <del></del> 250 |     |         |

| 25  | ThIA(RD)    | INTACK 1 to RD 1 Hold Time                             | 30             |     | 20              |     |         |

| 26  | ThIEI(RD)   | IEI Hold Time to RD 1                                  | 20             |     | 10              |     |         |

| 27  | TdRD(INT)   | RD † to INT † Delay                                    |                | 900 |                 | 800 |         |

| 28  | TdDCST      | Interrupt Daisy Chain Settle Time                      | 350            |     | 250             |     | 4       |

for the lowest priority peripheral, and TdIEI(IEO) for each peripheral separating them in the chain.

† Units in nanoseconds (ns).

• Timings are preliminary and subject to change.

<sup>A. The parameter for the devices in any particular daisy chain must meet the following constraint: The delay from INTACK to RD I must be greater than the sum of TdINA(IEO) for the highest priority peripheral, TsIEI(RD)</sup>

#### **Non-Z-BUS Interrupt Timing**

|     |              | ahal Brassadas                              | 4 MHz   | 6 MHz   |             |

|-----|--------------|---------------------------------------------|---------|---------|-------------|

| No. | Symbol       | Parameter                                   | Min Max | Min Max | Notes*†     |

| 29  | TdMW(INT)    | Message Write to INT Delay                  |         |         | 5,6         |

| 30  | TdDC(INT)    | Data Direction Change to INT Delay          |         |         | 5,7         |

| 31  | TdPMW(INT)   | Pattern Match (Write Case) to INT Delay     |         |         | 5           |

| 32- | —TdPMR(INT)— | —Pattern Match (Read Case) to INT Delay ——— |         |         | <del></del> |

| 33  | TdSC(INT)    | Status Compare to INT Delay                 |         |         | 5,7         |

| 34  | TdER(INT)    | Error to INT Delay                          |         |         | 5,7         |

| 35  | TdEM(INT)    | Empty to INT Delay                          |         |         | 5,7         |

| 36  | TdFL(INT)    | Full to INT Delay                           |         |         | 5,7         |

| 37  | TdSO(INT)    | State 0 to INT Delay                        |         |         | •           |

- NOTES:

5. Delay number is valid for State 0 only.

6. Write is from other side of FIO.

7. Write can be from either side, depending on programming of FIO.

- \* Timings are preliminary and subject to change. † Units in nanoseconds (ns).

## Non-Z-BUS Request/Wait Timing

|     |            |                                  | 41    | MHz     | 61  | MHz        |         |

|-----|------------|----------------------------------|-------|---------|-----|------------|---------|

| No. | Symbol     | Parameter                        | Min   | Max     | Min | Max        | Notes*† |

| 1   | TdRD(WT)   | CE i to WAIT Active              |       | 200     |     | 170        | _       |

| 2   | TdRD1(WT)  | RD1 f or WR1 f to WAIT Inactive  |       | 1000    |     | 1000       |         |

| 3   | TdACK(WT)  | ACKIN ↓ to WAIT Inactive         |       | 1000    |     | 1000       | 1       |

| 4   | -TdRD(REQ) | — RD 1 or WR 1 to REQ Inactive — |       | — 350 — |     | — 300 —    |         |

| 5   | TdRD1(REQ) | RDl 1 or WRl 1 to REQ Active     |       | 1000    |     | 1000       |         |

| 6   | TdACK(REQ) | ACKIN ↓ to REQ Active            |       | 1000    |     | 1000       |         |

| 7   | TdDAC(RD)  | DACK ↓ to RD ↓ or WR ↓           | 100   |         | 80  |            |         |

| 8-  | -TSU(WR)-  | — Data Setup Time to WR —————    | 200 — |         |     |            |         |

| 9   | Th(WR)     | Data Hold Time to WR             | 30    |         |     | 20         |         |

| 10  | TdDMA      | RD 1 to Valid Data               |       | 150     |     | 100        | 2       |

| 11  | TdDMA(DRH) | RD 1 to Data Not Valid           | 0     |         | 0   |            | 2       |

| 12  | TdDMA(DRZ) | RD 1 to Data Bus Float           |       | 70      |     | <b>4</b> 5 | 2       |

#### NOTES:

NOIES:

1. The delay is from DAC 1 for 3-Wire Input Handshake. The delay is from DAC 1 for 3-Wire Input Handshake.

2. Only when DACK is active.

\* Timings are preliminary and subject to change. † Units in nanoseconds (ns).

READ/WRITE OF DATA BUFFER REGISTER RD1 WRITE/READ OF DATA BUFFER REGISTER BY OTHER SIDE WAIT ACKIN INPUT/OUTPUT PORT **⑤** REQ (12) (10) DATA FROM FIG **--**| 10 DACK RD **③**

FIG WRITE TO DATA BUFFER REGISTER

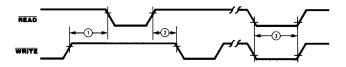

## Non-Z-BUS Reset Timing

|     |           |                                                                   | 4 MHz |     | 6 MHz |     |         |  |

|-----|-----------|-------------------------------------------------------------------|-------|-----|-------|-----|---------|--|

| No. | Symbol    | Parameter                                                         | Min   | Max | Min   | Max | Notes*† |  |

| 1   | TdWR(RD)  | Delay from WR ↑ to RD ↓                                           | 100   |     | 70    |     |         |  |

| 2   | TdRD(WR)  | Delay from $\overline{RD}$ 1 to $\overline{WR}$ 1                 | 100   |     | 70    |     |         |  |

| 3   | TwRD + WR | Width of $\overline{RD}$ and $\overline{WR}$ , both Low for Reset | 500   |     | 350   |     |         |  |

- NOTES:

\* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

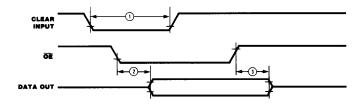

## Port 2 Side Operation

|     |           |                              | 4 MHz   | 6 1 | 6 MHz |         |

|-----|-----------|------------------------------|---------|-----|-------|---------|

| No. | Symbol    | Parameter                    | Min Max | Min | Max   | Notes*† |

| 1   | TwCLR     | Width of Clear to Reset FIFO | 700     | 700 |       |         |

| 2   | TdOE(DO)  | OE ↓ to Data Bus Driven      | 0       | 0   |       |         |

| 3   | TdOE(DRZ) | OE ↑ to Data Bus Float       |         |     |       |         |

- NOTES:

\* Timings are preliminary and subject to change.

† Units in nanoseconds (ns).

### FIO 2-Wire Handshake Timing

|     |               |                                                                                            | 41             | MHz | 6 MHz         |     |         |

|-----|---------------|--------------------------------------------------------------------------------------------|----------------|-----|---------------|-----|---------|

| No. | Symbol        | Parameter                                                                                  | Min            | Max | Min           | Max | Notes*† |

| 1   | TsDI(ACK)     | Data Input to ACKIN   to Setup Time                                                        | 50             |     | 50            |     |         |

| 2   | TdACKf(RFD)   | ĀCKIN ↓ to RFD ↓ Delay                                                                     | 0              | 500 | 0             | 500 |         |

| 3   | TdRFDr(ACK)   | RFD ↑ to ĀCKIN ↓ Delay                                                                     | 0              |     | 0             |     |         |

| 4   | -TsDO(DAV)-   | -Data Out to DAV   Setup Time-                                                             | <del></del> 50 |     | <del>25</del> |     |         |